ā╚╚▌ī¦║ĮŻ║

led’@╩ŠŲ┴┐žųŲŽĄĮyįOėŗ

ĪĪĪĪled’@╩ŠŲ┴┐žųŲļŖ┬ĘĪŻ×ķ┴╦╠ßĖ▀öĄō■▌ö│÷ą¦┬╩Ż¼▓╔ė├Ramtron╣½╦ŠĄ─ĦSPI╣”─▄─ŻēKĄ─VRS51L3074å╬Ų¼ÖCĪŻVRS51L3074Ą─ĢrńŖŅl┬╩×ķ40 M-HzŻ¼ųĖ┴Ņų▄Ų┌Č╠Ż¼╠Ä└Ē╦┘Č╚┐ņŻ¼ą¦┬╩Ė▀Ż╗╣żū„ļŖē║į┌3Ż«3 Vū¾ėęŻ¼Ą½╩Ū┐╔ęį╝µ╚▌5 VĪŻSST25VF016B╩Ūę╗┐ŅŠ▀ėąSPIĮė┐┌Ą─8ę²─_┤«ąąFlashĪŻ7 4LSl64×ķęŲ╬╗╝─┤µŲ„ĪŻ

ĪĪĪĪ1Īó VRS51L3074Ą─SPI╣”─▄─ŻēK

VRS51L3074Ą─SPIĢrńŖŅl┬╩┐╔ęįį┌SysClkŻ»2Ī½SysClkŻ»1024ĘČć·ā╚š{š¹Ż¼SPIĢrńŖŅl┬╩ūŅĖ▀┐╔ęį▀_ĄĮ20MHzĪŻ«öVRS51L3074ū„×ķSPIų„ÖCĢrŻ¼┐╔ęįī”SPI▀\ąą┐žųŲĪó┼õų├║═ĀŅæB▒O┐žęį╝░Ųõ╦¹Ą─ę╗ą®╣żū„ŁhŠ│▀MąąįOų├ĪŻ

┼õų├╝─┤µŲ„SPICONFIGŻ║ų„ę¬ī”Ų¼▀xą┼╠¢┐žųŲ─Ż╩ĮĪóSPIųąöÓ▀MąąįOų├ĪŻ

ĀŅæB╝─┤µŲ„SPISTATUSŻ║ų„ę¬ė├ė┌ī”SPI▀\ąąĀŅæBĄ─▒O┐žĪŻ

é„▌öūųķL╝─┤µŲ„SPISIZEŻ║įOų├é„▌öūųķLŻ¼▒Š╬─įOų├×ķ16╬╗Ż¼╝┤├┐┤╬▌ö│÷16╬╗öĄō■ĪŻ

┐žųŲ╝─┤µŲ„SPICTRLŻ║ī”SPIĢrńŖ╦┘┬╩ĪóĢrńŖŽÓ╬╗Ż»śOąįĪóŲ¼▀xą┼╠¢Ż¼ęį╝░SPIĢrńŖŅl┬╩▀MąąįOų├ĪŻ

öĄō■╝─┤µŲ„SPIRXTX0Ī½SPIRXTX3Ż║ė├ė┌ī”SPIĮė┐┌32╬╗╩š░lŠÅø_Ų„Ą─įLå¢Ż¼ī”öĄō■╝─┤µŲ„ł╠ąąīæ▓┘ū„╩ŪīóöĄō■╦═╚ļ░l╦═ŠÅø_Ų„ųąŻ¼ī”öĄō■╝─┤µŲ„ł╠ąąūx▓┘ū„╩ŪÅ─Įė╩šŠÅø_Ų„ųą╚Ī│÷╩šĄĮĄ─öĄō■ĪŻSPIĮė┐┌Ą─░l╦═║═Įė╩šŠÅø_Ų„Č╝▓╔ė├ļpŠÅø_ĮYśŗŻ¼Å─ė▓╝■╔Ž£p╔┘öĄō■ø_═╗▓ó╠ßĖ▀öĄō■é„▌öą¦┬╩ĪŻį┌ų„─Ż╩ĮŽ┬ī”SPIRXTX0╝─┤µŲ„ł╠ąąīæ╚ļ▓┘ū„īóåóäėSPIé„▌öĪŻ«öé„▌öūųĖ„ąąķL┤¾ė┌8ĢrŻ¼æ¬ūŅ║¾Ž“SPIRXTX0╝─┤µŲ„īæ╚ļĪŻ

ĪĪĪĪŽ“┤«ąąFlash▌ö╚ļ┐žųŲą┼╠¢║═öĄō■ĄžųĘ║¾Ż¼åóäė┤«ąąFlashé„▌ööĄō■Ż¼į┌SPIĢrńŖ“īäėŽ┬▌ö│÷’@╩ŠöĄō■Ż¼▓óŪę┐╔ęįė├å╬Ų¼ÖC─ŻöM┤«ąąFlashĢrńŖą┼╠¢┐žųŲ╚╬ęŌ╬╗öĄō■▌ö│÷ĪŻ

ĪĪĪĪ2Īó öĄō■▀xō±┐žųŲļŖ┬Ę

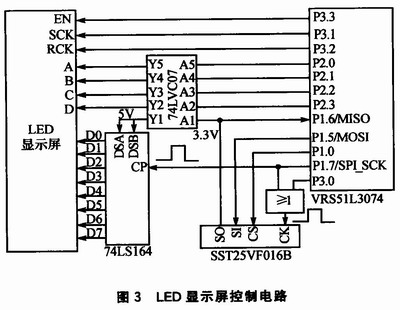

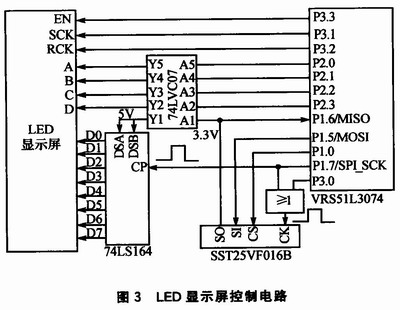

ĪĪĪĪled’@╩ŠŲ┴┐žųŲŽĄĮy╚ńłD3╦∙╩ŠŻ¼VRS51L3074å╬Ų¼ÖCā╚▓┐ūįĦŠ½┤_Ą─40 MHzš±╩ÄŲ„Ż¼▓╗ąĶę¬═Ō▓┐Š¦š±ļŖ┬Ę╠ß╣®ŽĄĮyĢrńŖĪŻöĄō■’@╩Š▓╔ė├ā╚┤µ×ķ16 MbĄ─SST25VF016BĪŻļpRAM╝╝ąg▌ö│÷’@╩ŠöĄō■Ą─Ģr║“Ż¼╩Ūīóā╔ēKRAMųąŽÓ═¼ĄžųĘĄ─ā╔éĆöĄō■═¼Ģr▌ö│÷Ż¼╦∙ęįŻ¼īóā╔ēKRAMĄ─’@╩ŠöĄō■┤µĘ┼į┌ę╗ēK┤«ąą┤µā”Ų„ųąĢrŻ¼┼╝ĄžųĘå╬į¬æ¬┤µā”RAM0Ą─öĄō■Ż¼ŲµĄžųĘå╬į¬┤µā”RAMlĄ─öĄō■Ż¼öĄō■▌ö│÷Ģr├┐┤╬▌ö│÷16╬╗öĄō■ĪŻ┤«ąą┤µā”Ų„║═å╬Ų¼ÖCĄ─╣żū„ļŖē║Č╝į┌3Ż«3 Vū¾ėęŻ¼Ą½╩ŪVRS51L3074┐╔ęį╝µ╚▌5VŻ¼║å╗»┴╦┐žųŲļŖ┬ĘĪŻ┐žųŲą┼╠¢║═’@╩ŠöĄō■į┌▌ö│÷ĄĮ╝─┤µŲ„74LS164║═’@╩ŠŲ┴Ą─Ģr║“Ż¼ąĶę¬ė├74LVC07▀MąąļŖŲĮ▐DōQĪŻ

┐žųŲŽĄĮy┐žųŲ’@╩ŠöĄō■▌ö│÷Ą─┴„│╠×ķŻ║

ó┘īóÆ▀├ĶŠĆąąĄžųĘ═©▀^P2Č╦┐┌Ą─Ą═4╬╗╦═Įoled’@╩ŠŲ┴ĪŻ

ó┌═©▀^’@╩ŠöĄō■į┌’@╩Šģ^ė“ųąĄ─╬╗ų├Ż¼ėŗ╦Ń’@╩ŠöĄō■į┌┤µā”Ų„ųąĄ─ĄžųĘŻ¼▓óėŗ╦Ń│÷öĄō■▀xō±Ą─╬╗öĄiĪŻ

ó█═©▀^å╬Ų¼ÖCP3Ż«0┐┌─ŻöMęŲ╬╗├}ø_Ż¼▌ö│÷ĄĮ┤«ąąFlashĢrńŖą┼╠¢Ż¼ęŲ╬╗├}ø_öĄė╔öĄō■▀xō±╬╗öĄiøQČ©ĪŻ╩╣▌ö│÷öĄō■«a╔·Õe╬╗Ż¼š²┤_Ąž▀xō±▌ö│÷’@╩ŠöĄō■ĪŻ

ó▄åóäėSPIūx╚Ī’@╩ŠöĄō■Ż¼SPIé„▌öūųķLįOų├×ķ16╬╗ĪŻ─ŻöM├}ø_ęčĮø▌ö│÷ĄĮ┤«ąąFlash╩╣öĄō■«a╔·┴╦Õe╬╗Ż¼▌ö│÷16╬╗öĄō■[DiŻ¼Di+1Ż¼ĪŁŻ¼D7Ż¼ĪŁŻ¼D15Ż¼D0Ż¼ĪŁŻ¼Di-1]Ż¼▌ö│÷ĄĮ’@╩ŠŲ┴Ą─öĄō■[D8+iŻ¼ĪŁŻ¼D15Ż¼D0Ż¼ĪŁŻ¼Di-1]į┌Ė▀8╬╗Ż¼Įø▀^ęŲ╬╗äé║├┐╔ęį┤µĘ┼į┌ęŲ╬╗╝─┤µŲ„ųąĪŻ├┐ąąĄ┌ę╗éĆöĄō■▌ö│÷║¾Ż¼┤╦ąąĖ„┴ąöĄō■Č╝ų▒Įė▌ö│÷ĪŻ

ó▌16╬╗öĄō■▌ö│÷═Ļ«ģ║¾Ż¼═©▀^P3.1─_«a╔·ę╗éĆSCK├}ø_Ż¼īóęŲ╬╗╝─┤µŲ„74LSl64ųąĄ─öĄō■▌ö│÷ęŲ╚ļĄĮå╬į¬░ÕĄ─┤«ąąęŲ╬╗╝─┤µŲ„74HC595ųąĪŻ

ó▐ųžÅ═Ą┌ó▄ų┴ó▌▓ĮŻ¼ų▒ĄĮę╗ąąöĄō■╚½▓┐▌ö│÷═Ļ«ģ║¾Ż¼ė╔P3Ż«2«a╔·ę╗éĆRCK├}ø_Ż¼ūx╚ĪĄ─ę╗ąąöĄō■īó▌ö│÷’@╩ŠŻ¼╚╗║¾Æ▀├ĶŠĆŽ┬ęŲę╗ąąĪŻ

ó▀ųžÅ═Ą┌ó┘ų┴ó▐▓ĮĪŻ

┤╦ļŖ┬Ęėą▀@śėÄūéĆ╠ž³cŻ║’@╩ŠöĄō■Å─┤«ąąFlash▌ö│÷║¾Ż¼▓╗Įøå╬Ų¼ÖCĄ─╠Ä└ĒŻ¼ų▒ĮėęįDMAĘĮ╩Į▌ö│÷ĄĮęŲ╬╗╝─┤µŲ„74LSl64Ż¼═¼ĢrīŹ¼F┤«▓ó▐DōQŻ¼╝╚╣Ø╩ĪöĄō■╠Ä└ĒĢrķgŻ¼ėų╠ßĖ▀’@╩Šą¦┬╩ĪŻį┌├┐ł÷öĄō■▌ö│÷ų«Ū░Ż¼═©▀^ą┼Žóį┌’@╩Šģ^ė“ųąĄ─ĄžųĘėŗ╦ŃöĄō■▀xō±╬╗öĄiŻ¼▓ó═©▀^P3Ż«OČ╦┐┌─ŻöMiéĆ├}ø_▌ö│÷ĄĮ┤«ąąFlashŻ¼ęŲ│÷i╬╗öĄō■Ż¼öĄō■«a╔·Õe╬╗Ż¼╩╣▌ö│÷’@╩ŠĄ─öĄō■į┌16╬╗▌ö│÷öĄō■Ą─Ė▀8╬╗Ż¼┐╔ęįų▒Įė┤µĘ┼į┌ęŲ╬╗╝─┤µŲ„ųąŻ¼▌ö│÷ĄĮ’@╩ŠŲ┴ĪŻęį║¾═¼ąąĖ„┴ąĄ─’@╩ŠöĄō■▌ö│÷ĢrŻ¼¤oąĶį┘▀MąąöĄō■▀xō±╬╗Ą─┼ąöÓŻ¼ų▒Įėīó’@╩ŠöĄō■Å─┤µā”Ų„ųą▌ö│÷ĄĮ’@╩ŠŲ┴ĪŻ

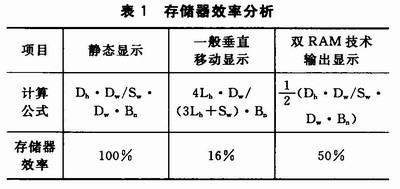

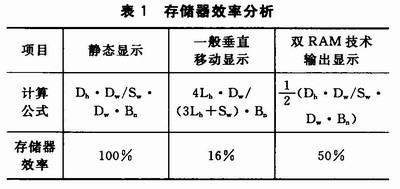

ĪĪĪĪ┤µā”Ų„ą¦┬╩Ęų╬÷╚ń▒Ē1╦∙┴ąĪŻ

ĪĪĪĪė╔▒Ē1┐╔ų¬Ż¼▓╔ė├ļpRAM╝╝ąg▌ö│÷’@╩Š┤¾┤¾╠ßĖ▀┴╦┤µā”Ų„ą¦┬╩Ż¼ĮĄĄ═┴╦’@╩ŠöĄō■┤µā”Ų„Ą─š╝ė├ĪŻ«ö’@╩Šą┼Žó┴┐▌^┤¾ĢrŻ¼äėæBöĄō■ĮM┐Ś╩╣ė├Ą─┤µā”Ų„▒╚▌^ČÓĪó└¹ė├┬╩Ą═Ż¼Č°▓╔ė├ļpRAM╝╝ągš²║├ĮŌøQ┴╦▀@éĆå¢Ņ}ĪŻę╗ēKRAM(ņoæB’@╩ŠĢr)Ą─┤µā”Ų„ą¦┬╩╩Ū100ŻźŻ¼ļpRAMĄ─ą¦┬╩╩Ū50ŻźĪŻ«öėąNēKRAMĢrŻ¼ą¦┬╩×ķ(N-1)Ż»NĪŻ

ßśī”łD3╦∙╩Š┐žųŲļŖ┬ĘŻ¼░┤ššöĄō■▌ö│÷┐žųŲ┴„│╠ŠÄīæ┴╦│╠ą“┤·┤aĪŻļSÖC’@╩Šę╗Ų┴ą┼ŽóŻ¼’@╩ŠöĄō■ęč░┤Ēśą“┤µā”į┌┤«ąąFlashųąĪŻ

Ēō┤aŻ║

╔Žę╗Ēō

1

2

3

Ž┬ę╗Ēō